The first carbon nanotube computer has 178 transistors and is 1-bit one-instruction set computer, later one is 16-bit (while the instruction set is 32-bit RISC-V).

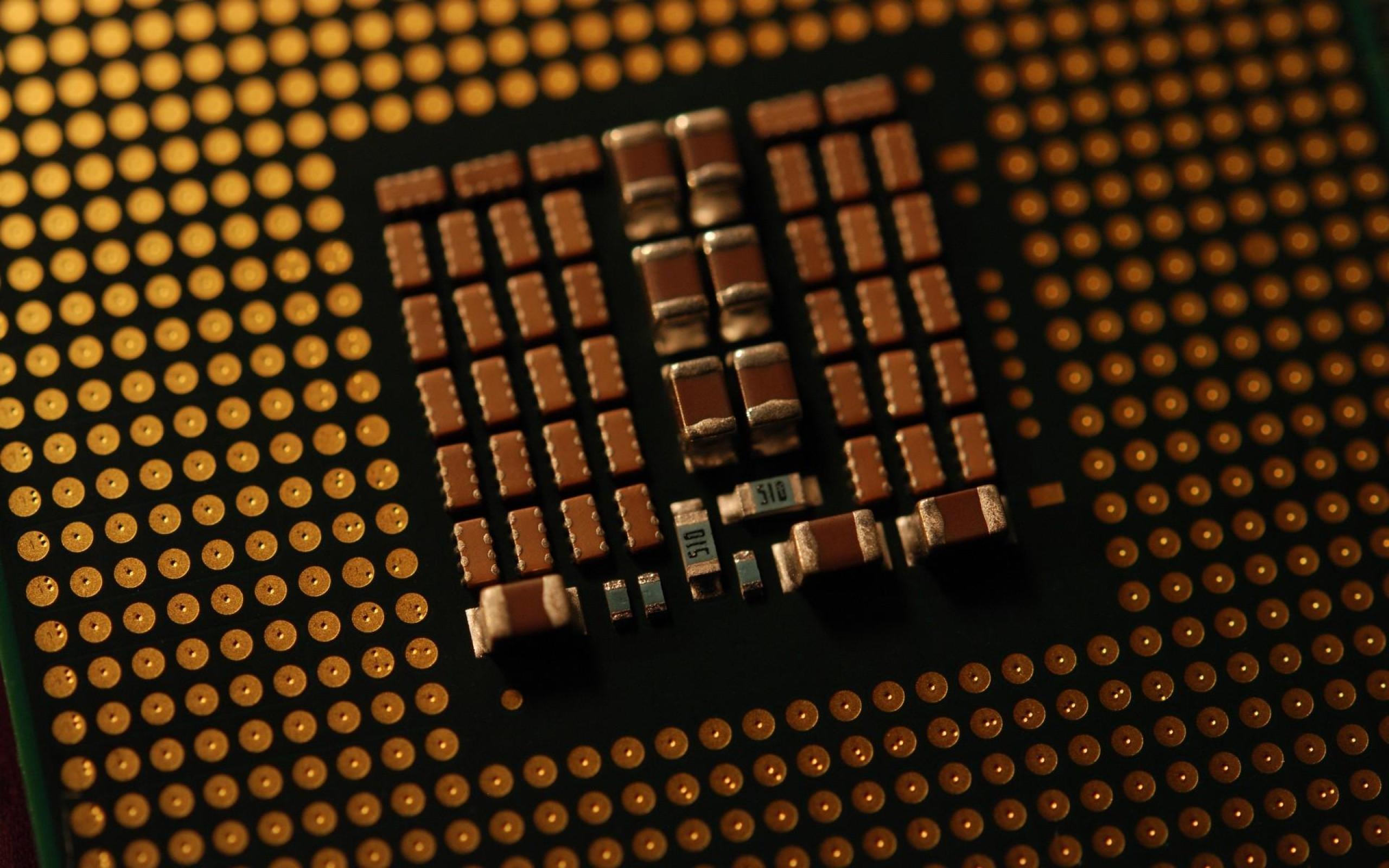

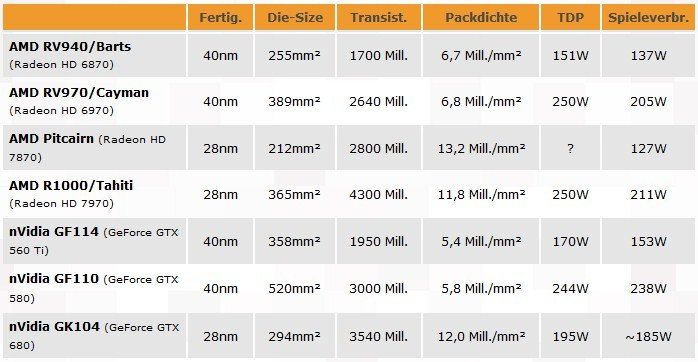

Early experimental solid state computers had as few as 130 transistors, but used large amounts of diode logic. In terms of computer systems that consist of numerous integrated circuits, the supercomputer with the highest transistor count as of 2016 is the Chinese-designed Sunway TaihuLight, which has for all CPUs/nodes combined "about 400 trillion transistors in the processing part of the hardware" and "the DRAM includes about 12 quadrillion transistors, and that's about 97 percent of all the transistors." To compare, the smallest computer, as of 2018 dwarfed by a grain of rice, has on the order of 100,000 transistors. As of 2020, the highest transistor count in any IC chip is a deep learning engine called the Wafer Scale Engine 2 by Cerebras, using a special design to route around any non-functional core on the device it has 2.6 trillion MOSFETs, manufactured using TSMC's 7 nm FinFET process. As of 2019, the highest transistor count in any IC chip was Samsung's 1 terabyte eUFS (3D-stacked) V-NAND flash memory chip, with 2 trillion floating-gate MOSFETs (4 bits per transistor). As of 2020, the highest transistor count in a graphics processing unit (GPU) is Nvidia's GA100 Ampere with 54 billion MOSFETs, manufactured using TSMC's 7 nm process. The transistor density (number of transistors per square millimetre) is more important than transistor size, since smaller transistors no longer necessarily mean improved performance, or an increase in the number of transistors.Īs of 2019, the largest transistor count in a commercially available microprocessor is 39.54 billion MOSFETs, in AMD's Zen 2 based Epyc Rome, which is a 3D integrated circuit (with eight dies in a single package) fabricated using TSMC's 7 nm FinFET semiconductor manufacturing process. TSMC and Samsung's 10 nm processes are somewhere between Intel's 14 nm and 10 nm processes in transistor density.

For example, GlobalFoundries' 7 nm processes are similar to Intel's 10 nm process, thus the conventional notion of a process node has become blurred. Since 2009, however, "node" has become a commercial name for marketing purposes that indicates new generations of process technologies, without any relation to gate length, metal pitch or gate pitch. The curve shows counts doubling every two years, per Simple ALU register, register and register, immediate cached operations could now complete in a single cycle this previously required at least 2 cycles.Microprocessors against dates of introduction. The pipeline itself received some attention as well. Furthermore more aggressive math algorithms were used to implement the new FPU yielding faster floating point calculations. 80387, 80287, etc.), the 80486 moved the unit on-die eliminating the external communication delays altogether. Whereas before a separately packaged math coprocessor was used (i.e. Various enhancements were also made to the bus interface including faster communication that required single clock cycle instead of multiple. This provided much needed faster access to recently used data and instructions. The 8 KB, 4-way set associative, write-back policy, cache was unified for both the data and instructions. To improve performance Intel introduced a new layer of cache on-die (previously various external extensions existed). Like its predecessor, the 80486 maintains full backwards object code comparability with the all previous x86 processors ( 80386, 80286, 80186, etc.). Architecture Main article: 80486 Microarchitectures

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed